## Development of a Custom Superconducting Qubit Control and Readout System

Rodolfo Carobene<sup>,1,2,3</sup>, Pietro Campana<sup>1,2,3</sup>, Marco Gobbo<sup>1,2,3</sup>, Danilo Labranca<sup>1,2,3</sup>, Roberto Moretti<sup>1,2,3</sup>, Luca Origo<sup>1,2,3</sup>, Sara Gamba<sup>1,2,3</sup>, Alessandro Cattaneo<sup>1,2,3</sup>, Hervè Corti<sup>1,2,3</sup>, Matteo Borghesi<sup>1,2,3</sup>, Marco Faverzani<sup>1,2,3</sup>, Elena Ferri<sup>1,2,3</sup>, Alessandro Candido<sup>5,6,9</sup>, Deborah Volpe<sup>8</sup>, Christian Conti<sup>8</sup>, Andrea De Simone<sup>8</sup>, Giuseppe La Capra<sup>8</sup>, Matteo Beretta<sup>4</sup>, Pietro Albicocco<sup>4</sup>, Angelo Nucciotti<sup>1,2,3</sup>, Stefano Carrazza,<sup>5,6,7</sup>, Fabrizio Riente<sup>8</sup>, Claudio Gatti<sup>4</sup>, Andrea Giachero<sup>1,2,3</sup>

- 1. University of Milano-Bicocca, Department of Physics, Piazza della Scienza 3, 20126 Milano, Italy

- 2. INFN Milano-Bicocca, Piazza della Scienza 3, 20126 Milano, Italy

- 3. Bicocca Quantum Technologies Centre (BiQuTe), Piazza della Scienza 3, 20126 Milano, Italy

- 4. INFN Laboratori Nazionali di Frascati, 00044 Frascati, Roma, Italy

- 5. University of Milan, Department of Physics, Via Celoria 16, 20133 Milano, Italy

- 6. INFN Sezione di Mllano, Via Celoria 16, 20133 Milano, Italy

- 7. TII, Masdar City, Abu Dhabi , United Arab Emirates

- 8. Department of Electronics and Telecommunications, Politecnico di Torino, 10129 Torino, Italy

- 9. CERN, Theoretical Physics Department, CH-1211 Geneva 23, Switzerland

**Abstract**: We investigate the use of Radio-Frequency System on Chip (RFSoC) FPGA boards to build a custom control system for superconducting qubits control. RFSoC boards offer the benefits of being cost-efficient, compact, and fully configurable.

In recent years, superconducting quantum devices have made significant advancements, becoming viable instruments for quantum computing and quantum sensing. To characterize, develop, and control these devices, instruments capable of synthesizing fast pulses with arbitrary waveforms within the microwave frequency range are essential. Due to the rapid expansion of the field, the requirements are constantly evolving, making it challenging to establish fixed specifications for these instruments. Thus, beyond pure performance, flexibility is crucial.

Traditionally, generating pulses at these frequencies involved up and down-conversion schemes, combining lower-frequency pulses with high-frequency tones. However, this technique suffers from poor scalability and introduces multiple potential failure points, complicating experiments. While a few companies offer proprietary hardware solutions to address these issues, their expensive products often comprise the same discrete components available on the market at a fraction of the cost.

Within NQSTI spoke 6, we previously introduced Qibosoq [1, 2, 3], an open-source software tool enabling the use of RFSoC FPGAs as a cost-effective solution for the control and readout of superconducting qubits. RFSoC boards are extremely compact, fully configurable, and offer high speed and frequency bandwidth. For instance, with the ZCU216 [4], an AMD RFSoC that is becoming a standard in quantum computing, no additional instruments are needed to control multiple transmons in the 0-10 GHz range, and the board itself can be repurposed for different applications and type of qubits. Qibosoq leverages the open-source firmware of QICK [5, 6], developed by FNAL, thus inheriting its benefits and limitations. Notably, outsourcing firmware development has slowed the addition of features not widely requested by the community.

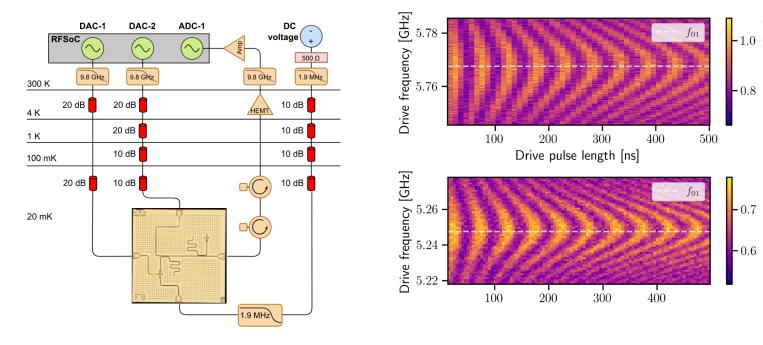

Over the past year, we have pursued two parallel approaches. Firstly, we tested Qibosoq on various quantum devices in different laboratories. In particular, we successfully characterised a chip with two qubits in the cryogenic laboratory of Milano Bicocca [7]. This chip, comprising a flux-tunable qubit and a fixed-frequency qubit, was designed by our team, and Qibosoq demonstrated its capability to effectively characterize and control it. In this case we used a RFSoC4xs2 board, which required the use of an external DC voltage generator to control the frequency of the flux-tunable transmon. In the following figures, the setup of the measurement is shown, as well as the Rabi oscillations of the two qubits.

Secondly, we began modifying the original QICK firmware to extend its functionalities. In collaboration with the Politecnico di Torino, we are enhancing the internal trigger signals to optimize performance and resource utilization. Additionally, we are integrating a RISC-V softcore directly into the FPGA [8], enabling the development of a real-time, flexible trigger system directly on the board. An effort to write a completely new firmware for continuous acquisition is also started at the LNF laboratories. This will enable the use of RFSoC boards for longer experiments not executed in pulsed mode.

On the left, the experimental setup used for the chip characterization. On the right, the chevron plot for Rabi oscillations for two qubits: one flux tunable (bottom) and one at fixed-frequency (top)

## References

- [1] R.Carobene et al.,"Qibosoq: an open-source framework for quantum circuit RFSoC programming", arXiv:2310.05851 (2023);

- [2] S.Efthymiou et al., "Qibo: a framework for quantum simulation with hardware acceleration", Quantum Sci. Technol. 7 015018 (2021);

- [3] S.Efthymiou et al., "Qibolab: an open-source hybrid quantum operating system", arXiv:2308.06313 (2023);

- [4] AMD, https://www.xilinx.com/products/boards-and-kits/zcu216.html

- [5] L.Stefanazzi et al., "The QICK (Quantum Instrumentation Control Kit): Readout and control for qubits and detectors", arXiv:2110.00557 (2021);

- [6] L.Stefanazzi et al., "Experimental advances with the QICK (Quantum Instrumentation Control Kit) for superconducting quantum hardware", arXiv:2311.17171 (2023);

- [7] R.Moretti et al., "Transmon qubit modeling and characterization for Dark Matter search", arXiv:2409.05988 (2024);

- [8] L.Poli et al., "Design and Implementation of a RISC V Processor on FPGA", DOI: 10.1109/MSN53354.2021.00037 (2024);